Digital Signal Processing Implementation

using the TMS320C6000 processors

Seiten

2000

Prentice-Hall

978-0-201-61916-4 (ISBN)

Prentice-Hall

978-0-201-61916-4 (ISBN)

- Titel ist leider vergriffen;

keine Neuauflage - Artikel merken

This work is aimed first-time users of digital signal processing who need to implement systems with high-performance TI processors. It describes the architecture of the processors and the associated tools, and provides examples.

This text is a vital accessory for both students and professionals using the latest TI DSP processors. It is ideal for use on advanced DSP or industrial education courses covering the TMS320C6x processor. This text is aimed at DSP users who need to implement systems with the new family of high-performance TI processors. It describes the architecture of the processors as well as detailing the associated tools and providing practical examples. Using pragmatic experiments based on common DSP operations, this book enables the reader to make real-time applications work in a relatively short period of time.

This text is a vital accessory for both students and professionals using the latest TI DSP processors. It is ideal for use on advanced DSP or industrial education courses covering the TMS320C6x processor. This text is aimed at DSP users who need to implement systems with the new family of high-performance TI processors. It describes the architecture of the processors as well as detailing the associated tools and providing practical examples. Using pragmatic experiments based on common DSP operations, this book enables the reader to make real-time applications work in a relatively short period of time.

1. Introduction. 2. The TMS320C6000 Architecture. 3. Software Development Tools and TMS320C6201 EVM Overview. 4. Optimization. 5. Finite Impulse Response (FIR) Filter Implementation. 6. Infinite Impulse Response (IIR) Filter Implementation. 8. Goertzel Algorithm Implementation. 9. Implementation of the Discrete Cosine Transform. Appendix A: Optimization of 1-D DCT and IDCT. Appendix B: Block Memory Display.

| Verlagsort | Harlow |

|---|---|

| Sprache | englisch |

| Maße | 160 x 242 mm |

| Gewicht | 530 g |

| Themenwelt | Mathematik / Informatik ► Informatik |

| Technik ► Nachrichtentechnik | |

| ISBN-10 | 0-201-61916-4 / 0201619164 |

| ISBN-13 | 978-0-201-61916-4 / 9780201619164 |

| Zustand | Neuware |

| Informationen gemäß Produktsicherheitsverordnung (GPSR) | |

| Haben Sie eine Frage zum Produkt? |

Mehr entdecken

aus dem Bereich

aus dem Bereich

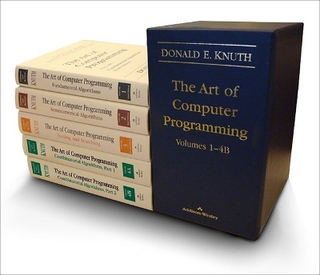

Media-Kombination (2023)

Addison Wesley

CHF 409,95

Media-Kombination (2025)

bSD Verlag - Haus der Bundespressekonferenz / 4103

CHF 87,35

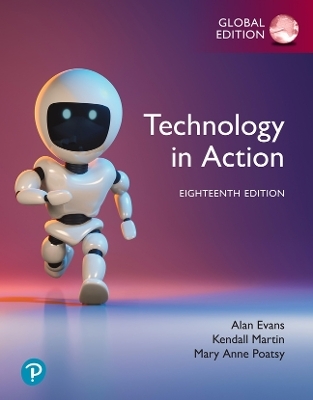

Media-Kombination (2024)

Pearson Education Limited

CHF 144,40