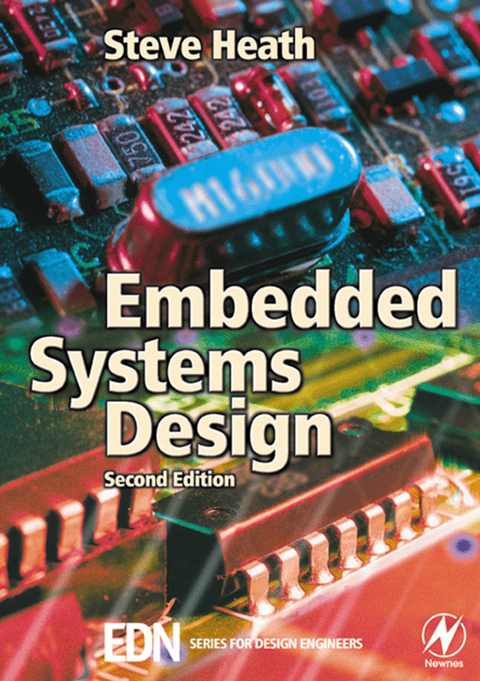

Embedded Systems Design (eBook)

430 Seiten

Elsevier Science (Verlag)

978-0-08-047756-5 (ISBN)

* A practical introduction to the hottest topic in modern electronics design

* Covers hardware, interfacing and programming in one book

* New material on Embedded Linux for embedded internet systems

In this new edition the latest ARM processors and other hardware developments are fully covered along with new sections on Embedded Linux and the new freeware operating system eCOS. The hot topic of embedded systems and the internet is also introduced. In addition a fascinating new case study explores how embedded systems can be developed and experimented with using nothing more than a standard PC.* A practical introduction to the hottest topic in modern electronics design* Covers hardware, interfacing and programming in one book* New material on Embedded Linux for embedded internet systems

Cover 1

Contents 5

Preface 17

Acknowledgements 19

1 What is an embedded system? 21

What is an embedded system? 22

Replacement for discrete logic-based circuits 22

Provide functional upgrades 23

Provide easy maintenance upgrades 23

Improves mechanical performance 23

Protection of intellectual property 24

Replacement for analogue circuits 24

Inside the embedded system 28

Processor 28

Memory 28

Peripherals 29

Software 30

Algorithms 30

Examples 31

Microcontroller 31

Expanded microcontroller 33

Microprocessor based 34

Board based 34

2 Embedded processors 35

8 bit accumulator processors 36

Register models 36

8 bit data restrictions 37

Addressing memory 38

System integrity 39

Example 8 bit architectures 39

Z80 39

Z80 programming model 41

MC6800 42

Microcontrollers 43

MC68HC05 43

MC68HC11 43

Architecture 45

Data processors 45

Complex instructions, microcode and nanocode 45

INTEL 80286 48

Architecture 48

Interrupt facilities 49

Instruction set 50

80287 floating point support 50

Feature comparison 50

INTEL 80386DX 50

Architecture 50

Interrupt facilities 52

Instruction set 52

80387 floating point coprocessor 53

Feature comparison 53

INTEL 80486 54

Instruction set 55

Intel 486SX and overdrive processors 55

Intel Pentium 56

Pentium Pro 58

Multiple branch prediction 58

Data flow analysis 58

Speculative execution 58

The MMX instructions 59

The Pentium II 60

Motorola MC68000 60

The MC68000 hardware 61

Address bus 61

Data bus 61

Function codes 62

Interrupts 63

Error recovery and control signals 64

Motorola MC68020 64

The programmer’s model 66

Bus interfaces 69

Motorola MC68030 70

The MC68040 71

The programming model 73

Integrated processors 74

RISC processors 77

The 80/20 rule 77

The initial RISC research 78

The Berkeley RISC model 79

Sun SPARC RISC processor 80

Architecture 80

Interrupts 80

Instruction set 81

The Stanford RISC model 82

The MPC603 block diagram 83

The ARM RISC architecture 85

The ARM register set 85

Exceptions 86

The Thumb instructions 87

Digital signal processors 88

DSP basic architecture 89

Choosing a processor 92

Does it have enough performance? 92

3 Memory systems 94

Memory technologies 94

DRAM technology 96

Video RAM 97

SRAM 97

Pseudo-static RAM 98

Battery backed-up SRAM 98

EPROM and OTP 98

Flash 99

EEPROM 99

Memory organisation 99

By 1 organisation 100

By 4 organisation 101

By 8 and by 9 organisations 101

By 16 and greater organisations 101

Parity 101

Parity initialisation 102

Error detecting and correcting memory 102

Access times 103

Packages 103

Dual in line package 104

Zig–zag package 104

SIMM and DIMM 104

SIP 105

DRAM interfaces 105

The basic DRAM interface 105

Page mode operation 106

Page interleaving 106

Burst mode operation 107

EDO memory 107

DRAM refresh techniques 108

Distributed versus burst refresh 108

Software refresh 109

RAS only refresh 109

CAS before RAS (CBR) refresh 109

Hidden refresh 109

Memory management 110

Disadvantages of memory management 112

Segmentation and paging 113

Memory protection units 117

Cache memory 119

Cache size and organization 120

Optimizing line length and cache size 124

Logical vs physical caches 125

Unified versus Harvard caches 126

Cache coherency 126

Case 1: write-through 128

Case 2: write-back 129

Case 3: no caching of write cycles 130

Case 4: write buffer 130

Bus snooping 131

The MESI protocol 136

The MEI protocol 137

Burst interfaces 138

Meeting the interface needs 139

Big and little endian 141

Dual port and shared memory 142

Bank switching 143

Memory overlays 144

Shadowing 144

Example interfaces 145

MC68000 asynchronous bus 145

M6800 synchronous bus 147

The MC68040 burst interface 148

4 Basic peripherals 151

Parallel ports 151

Multi-function I/O ports 152

Pull-up resistors 153

Timer/counters 153

Types 154

8253 timer modes 154

Interrupt on terminal count 154

Programmable one-shot 154

Rate generator 156

Square wave rate generator 156

Software triggered strobe 156

Hardware triggered strobe 157

Generating interrupts 157

MC68230 modes 157

Timer processors 158

Real-time clocks 159

Simulating a real-time clock in software 160

Serial ports 160

Serial peripheral interface 162

I2C bus 163

Read and write access 165

Addressing peripherals 166

Sending an address index 167

Timing 168

Multi-master support 169

M-Bus (Motorola) 170

What is an RS232 serial port? 170

Asynchronous flow control 173

Modem cables 175

Null modem cables 175

XON-XOFF flow control 178

UART implementations 178

8250/16450/16550 178

The interface signals 179

The Motorola MC68681 182

DMA controllers 183

A generic DMA controller 184

Operation 184

DMA controller models 186

Single address model 186

Dual address model 187

1D model 188

2D model 188

3D model 189

Channels and control blocks 189

Sharing bus bandwidth 191

DMA implementations 193

Intel 8237 193

Motorola MC68300 series 193

Using another CPU with firmware 194

5 Interfacing to the analogue world 195

Analogue to digital conversion techniques 195

Quantisation errors 196

Sample rates and size 196

Irregular sampling errors 197

Nyquist’s theorem 199

Codecs 199

Linear 199

A-law and 199

-law 199

PCM 200

DPCM 200

ADPCM 201

Power control 201

Matching the drive 201

Using H bridges 203

Driving LEDs 204

Interfacing to relays 204

Interfacing to DC motors 205

Software only 206

Using a single timer 207

Using multiple timers 208

6 Interrupts and exceptions 209

What is an interrupt? 209

The spaghetti method 210

Using interrupts 211

Interrupt sources 212

Internal interrupts 212

External interrupts 212

Exceptions 212

Software interrupts 213

Non-maskable interrupts 213

Recognising an interrupt 214

Edge triggered 214

Level triggered 214

Maintaining the interrupt 214

Internal queuing 214

The interrupt mechanism 215

Stack-based processors 215

MC68000 interrupts 216

RISC exceptions 218

Synchronous precise 219

Synchronous imprecise 219

Asynchronous precise 219

Asynchronous imprecise 220

Recognising RISC exceptions 220

Enabling RISC exceptions 222

Returning from RISC exceptions 222

The vector table 222

Identifying the cause 223

Fast interrupts 223

Interrupt controllers 225

Instruction restart and continuation 225

Interrupt latency 226

Do’s and Don’ts 229

Always expect the unexpected interrupt 229

Don't expect too much from an interrupt 229

Use handshaking 230

Control resource sharing 230

Beware false interrupts 231

Controlling interrupt levels 231

Controlling stacks 231

7 Real-time operating systems 232

What are operating systems? 232

Operating system internals 234

Multitasking operating systems 235

Context switching, task tables, and kernels 235

Time slice 243

Pre-emption 244

Co-operative multitasking 244

Scheduler algorithms 245

Rate monotonic 245

Deadline monotonic scheduling 247

Priority guidelines 247

Priority inversion 247

Disabling interrupts 247

Message queues 248

Waiting for a resource 249

VMEbus interrupt messages 249

Fairness systems 251

Tasks, threads and processes 251

Exceptions 252

Memory model 253

Memory allocation 253

Memory characteristics 254

Example memory maps 255

Memory management address translation 259

Bank switching 262

Segmentation 263

Virtual memory 263

Choosing an operating system 264

Assembler versus high level language 265

ROMable code 265

Scheduling algorithms 265

Pre-emptive scheduling 266

Modular approach 266

Re-entrant code 267

Cross-development platforms 267

Integrated networking 267

Multiprocessor support 267

Commercial operating systems 268

pSOS+ 268

pSOS+ kernel 268

pSOS multiprocessor kernel 269

pREPC+ runtime support 269

pHILE+ file system 270

pNA+ network manager 270

pROBE+ system level debugger 270

XRAY+ source level debugger 270

OS-9 270

VXWorks 271

VRTX-32 271

IFX 272

TNX 272

RTL 272

RTscope 272

MPV 272

LynxOS-POSIX conformance 272

Windows NT 274

Windows NT characteristics 275

Process priorities 276

Interrupt priorities 277

Resource protection 278

Protecting memory 278

Protecting hardware 278

Coping with crashes 279

Multi-threaded software 279

Addressing space 280

Virtual memory 281

The internal architecture 281

Virtual memory manager 282

User and kernel modes 282

Local procedure call (LPC) 283

The kernel 283

File system 283

Network support 284

I/O support 284

HAL approach 284

Linux 285

Origins and beginnings 285

Inside Linux 288

The Linux file system 289

The physical file system 290

Building the file system 291

The file system 292

Disk partitioning 294

The /proc file system 297

Data caching 297

Multi-tasking systems 298

Multi-user systems 298

Linux software structure 299

Processes and standard I/O 300

Executing commands 301

Physical I/O 302

Memory management 303

Linux limitations 303

eLinux 304

8 Writing software for embedded systems 308

The compilation process 308

Compiling code 309

The pre-processor 310

Compilation 313

as assembler 315

Linking and loading 316

Symbols, references and relocation 316

Id linker/loader 317

Native versus cross-compilers 318

Run-time libraries 318

Processor dependent 318

I/O dependent 319

System calls 319

Exit routines 319

Writing a library 320

Creating a library 320

Device drivers 326

Debugger supplied I/O routines 326

Run-time libraries 327

Using alternative libraries 327

Linking additional libraries 327

Linking replacement libraries 327

Using a standard library 327

Porting kernels 328

Board support 328

Rebuilding kernels for new configurations 329

configA11.h 330

config.h 330

usrConfig.c 330

pSOSystem+ 332

C extensions for embedded systems 333

#pragma interrupt func2 333

#pragma pure_function func2 334

#pragma no_side_effects func2 334

#pragma no_return func2 334

#pragma mem_port int2 334

asm and _ _asm 334

Downloading 336

Serial lines 336

EPROM and FLASH 337

Parallel ports 337

From disk 337

Ethernet 338

Across a common bus 338

9 Emulation and debugging techniques 341

Debugging techniques 341

High level language simulation 341

Low level simulation 342

Onboard debugger 343

Task level debugging 345

Symbolic debug 345

Emulation 347

Optimisation problems 348

Xray 352

The role of the development system 355

Floating point and memory management functions 355

Emulation techniques 356

JTAG 357

OnCE 357

BDM 358

10 Buffering and other data structures 359

What is a buffer? 359

Latency 361

Timing tolerance 361

Memory size 362

Code complexity 362

Linear buffers 362

Directional buffers 364

Single buffer implementation 364

Double buffering 366

Buffer exchange 368

Linked lists 369

FIFOs 370

Circular buffers 371

Buffer underrun and overrun 372

Allocating buffer memory 373

malloc() 373

Memory leakage 374

Stack frame errors 374

Failure to return memory to the memory pool 375

Housekeeping errors 375

Wrong memory specification 376

11 Memory and performance trade-offs 377

The effect of memory wait states 377

Scenario 1 „ Single cycle processor with large external memory 378

Scenario 2 „ Reducing the cost of memory access 380

Using registers 380

Using caches 381

Preloading caches 382

Using on-chip memory 383

Using DMA 383

Making the right decisions 383

12 Software examples 385

Benchmark example 385

Creating software state machines 388

Priority levels 392

Explicit locks 393

Interrupt service routines 393

Setting priorities 395

Task A highest priority 395

Task C highest priority 396

Using explicit locks 396

Round-robin 396

Using an ISR routine 397

13 Design examples 399

Buglar alarm system 399

Design goals 399

Development strategy 400

Software development 400

Cross-compilation and code generation 403

Porting to the final target system 405

Generation of test modules 405

Target hardware testing 405

Future techniques 405

Relevance to more complex designs 406

The need for emulation 406

Digital echo unit 407

Creating echo and reverb 407

Design requirements 410

Designing the memory structures 411

The software design 412

Multiple delays 414

Digital or analogue adding 415

Microprocessor selection 15

The overall system design 416

14 Real- time without a RTOS 418

Choosing the software environment 418

Deriving real-time performance from a non-real-time system 420

Choosing the hardware 421

Scheduling the data sampling 422

Sampling the data 425

Controlling from an external switch 426

Driving an external LED display 428

Testing 428

Problems 430

Saving to hard disk 430

Data size restrictions and the use of a RAM disk 430

Timer calculations and the compiler 431

Data corruption and the need for buffer flushing 431

Program listing 433

Index 442

| Erscheint lt. Verlag | 30.10.2002 |

|---|---|

| Sprache | englisch |

| Themenwelt | Sachbuch/Ratgeber |

| Mathematik / Informatik ► Informatik ► Theorie / Studium | |

| Mathematik / Informatik ► Mathematik ► Computerprogramme / Computeralgebra | |

| Technik ► Elektrotechnik / Energietechnik | |

| ISBN-10 | 0-08-047756-9 / 0080477569 |

| ISBN-13 | 978-0-08-047756-5 / 9780080477565 |

| Haben Sie eine Frage zum Produkt? |

Kopierschutz: Adobe-DRM

Adobe-DRM ist ein Kopierschutz, der das eBook vor Mißbrauch schützen soll. Dabei wird das eBook bereits beim Download auf Ihre persönliche Adobe-ID autorisiert. Lesen können Sie das eBook dann nur auf den Geräten, welche ebenfalls auf Ihre Adobe-ID registriert sind.

Details zum Adobe-DRM

Dateiformat: PDF (Portable Document Format)

Mit einem festen Seitenlayout eignet sich die PDF besonders für Fachbücher mit Spalten, Tabellen und Abbildungen. Eine PDF kann auf fast allen Geräten angezeigt werden, ist aber für kleine Displays (Smartphone, eReader) nur eingeschränkt geeignet.

Systemvoraussetzungen:

PC/Mac: Mit einem PC oder Mac können Sie dieses eBook lesen. Sie benötigen eine

eReader: Dieses eBook kann mit (fast) allen eBook-Readern gelesen werden. Mit dem amazon-Kindle ist es aber nicht kompatibel.

Smartphone/Tablet: Egal ob Apple oder Android, dieses eBook können Sie lesen. Sie benötigen eine

Geräteliste und zusätzliche Hinweise

Buying eBooks from abroad

For tax law reasons we can sell eBooks just within Germany and Switzerland. Regrettably we cannot fulfill eBook-orders from other countries.

aus dem Bereich