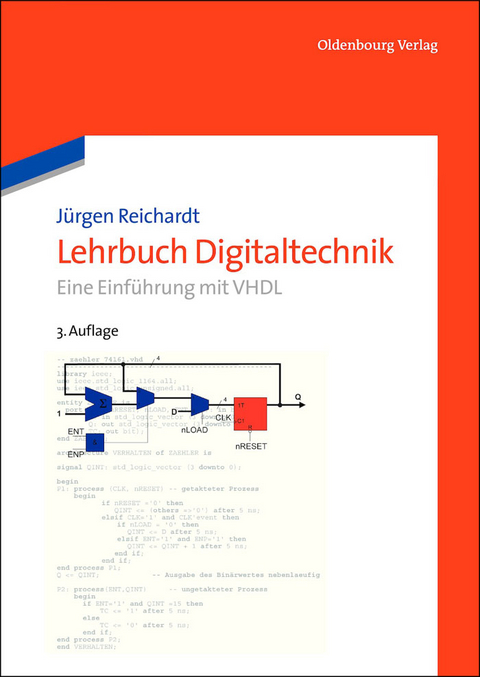

Lehrbuch Digitaltechnik (eBook)

412 Seiten

De Gruyter (Verlag)

978-3-486-75387-5 (ISBN)

This textbook provides a step-by-step introduction to the important elements of the VHDL hardware descriptive language in tandem with the fundamental principles of digital circuit design, ensuring that the reader has the knowledge required to understand and design simple digital systems.

Jürgen Reichardt, Hamburg

Vorwort zur 3. Auflage V 5

1 Einleitung 15

1.1 Die Hardwarebeschreibungssprache VHDL 17

1.2 Digitale und Analoge Signale 18

1.3 Digitale Systeme 19

1.4 Gliederung des Buches 22

1.5 Vertiefende Aufgaben 23

2 Modellierung digitaler Schaltungen 25

2.1 Lernziele 25

2.2 Entwurfssichten und Abstraktionsebenen 25

2.3 Modellierung mit Hardwarebeschreibungssprachen 28

2.3.1 Datenflussmodelle 29

2.3.2 Strukturmodelle 29

2.3.3 Verhaltensmodelle 30

2.4 Kombinatorische und getaktete Logik 30

2.4.1 Eigenschaften kombinatorischer Logik 31

2.4.2 Eigenschaften getakteter Logik 31

2.4.3 Modellierung auf Register-Transfer-Ebene 32

2.5 Entwurfsmethodik für programmierbare digitale Schaltungen 33

2.6 Vertiefende Aufgaben 34

3 Boole’sche Algebra 35

3.1 Lernziele 35

3.2 Schaltvariable und Schaltfunktionen, Signale 35

3.3 Elementare Schaltfunktionen 36

3.3.1 Die NICHT-Schaltfunktion (Inversion) 37

3.3.2 Die UND-Schaltfunktion (Konjunktion) 37

3.3.3 Die ODER-Schaltfunktion (Disjunktion) 38

3.3.4 Boole’sche Funktionen mit mehreren Eingängen 38

3.4 Rechenregeln der Schaltalgebra 39

3.4.1 Theoreme 39

3.4.2 Kommutativgesetze 40

3.4.3 Assoziativgesetze 40

3.4.4 Distributivgesetze 41

3.4.5 De Morgan’sche Gesetze 42

3.4.6 Vereinfachungsregeln 42

3.5 Vollständige Systeme 43

3.5.1 Das Dualitätsprinzip 43

3.5.2 NAND- und NOR-Gatter 44

3.6 Normalformen 46

3.6.1 Disjunktive Normalform (DNF) 47

3.6.2 Konjunktive Normalform (KNF) 47

3.7 Realisierung von Schaltfunktionen mit Wahrheitstabellen 48

3.7.1 SOP- und POS-Darstellungen von Wahrheitstabellen in programmierbaren Bausteinen mit UND/ODER-Logik 50

3.7.2 Look-Up-Tabellen 50

3.8 XOR- und XNOR-Logik 51

3.8.1 SOP- und POS-Darstellungen 51

3.8.2 XOR- und XNOR-Regeln und Gesetze 51

3.8.3 XOR- und XNOR-Logik mit mehr als zwei Eingängen 52

3.9 Vorrangregeln 53

3.10 Schaltsymbole 54

3.11 Implementierung von Schaltfunktionen mit Multiplexern 57

3.12 Analyse von Schaltnetzen 59

3.13 Vertiefende Aufgaben 61

4 VHDL-Einführung I 65

4.1 Lernziele 65

4.2 Syntaxnotation 65

4.3 Der Aufbau eines VHDL-Modells 66

4.3.1 Beschreibung einer entity 67

4.3.2 Aufbau einer architecture 69

4.3.3 Nebenläufige Signalzuweisungen 70

4.3.4 Logikoperatoren in VHDL 71

4.4 VHDL-Testbenches 78

4.5 Vertiefende Aufgaben 81

5 Zahlensysteme in der Digitaltechnik 83

5.1 Lernziele 84

5.2 Polyadische Zahlensysteme 84

5.3 Umwandlung zwischen Zahlensystemen 86

5.4 Addition und Subtraktion vorzeichenloser Dualzahlen 88

5.5 Darstellung negativer Zahlen 90

5.5.1 Eigenschaften des 2er-Komplementzahlensystems 91

5.5.2 Addition und Subtraktion im 2er-Komplementzahlensystem 94

5.6 Darstellung rationaler Zahlen 96

5.6.1 Festkommadarstellung im Q-Format 96

5.6.2 Gleitkommadarstellung 99

5.7 Vertiefende Aufgaben 100

6 Logikminimierung 103

6.1 Lernziele 103

6.2 Minimierung mit KV-Tafeln 103

6.2.1 Disjunktive Minimalform (DMF) 104

6.2.2 Konjunktive Minimalform (KMF) 112

6.2.3 Output-Don’t-Care-Terme 113

6.2.4 Grenzen der zweistufigen Minimierung 116

6.3 Softwarealgorithmen zur zweistufigen Minimierung 122

6.3.1 Quine-McCluskey-Algorithmus 122

6.3.2 Espresso-Algorithmus 123

6.4 Minimierungskonzepte für FPGAs 123

6.5 Vertiefende Aufgaben 125

7 VHDL-Einführung II 129

7.1 Lernziele 129

7.2 Das VHDL-Prozesskonzept 129

7.3 Ereignisgesteuerte Simulatoren 131

7.4 Verzögerungsmodelle 134

7.5 Sequenzielle Anweisungen in Prozessen 136

7.5.1 case-Anweisung 136

7.5.2 if-Anweisung 138

7.6 Prozesse ohne Sensitivityliste 142

7.7 Verwendung von Variablen in Prozessen 142

7.8 Modellierungsbeispiel 143

7.9 Vertiefende Aufgaben 147

8 Codes 149

8.1 Lernziele 149

8.2 Charakterisierung und Klassifizierung 149

8.3 Zahlencodes 150

8.4 Code für die Längen- und Winkelmesstechnik 154

8.5 Methoden der Fehlererkennung und -korrektur 156

8.6 Vertiefende Aufgaben 159

9 Physikalische Implementierung und Beschaltung von Logikgattern 161

9.1 Lernziele 161

9.2 Logikgatter in CMOS-Technologie 161

9.2.1 CMOS-Technologie und Kennlinien der MOS-Transistoren 161

9.2.2 Aufbau und Kennlinien eines CMOS-Inverters 163

9.2.3 Pegelbereiche digitaler Logikfamilien 166

9.3 Logikzustände und elektrische Pegel 167

9.4 Statische CMOS-Logikgatter 169

9.5 Beschaltung von Gatterausgängen 171

9.5.1 Standardausgang 171

9.5.2 Open-Drain- / Open-Collector-Ausgang 172

9.5.3 Three-State-Ausgang 175

9.6 VHDL-Modellierung mit den Datentypen std_ulogic und std_logic 177

9.6.1 Mehrwertige Datentypen 177

9.6.2 Datentypen mit Auflösungsfunktion 178

9.6.3 VHDL-Modellierungsbeispiele 180

9.7 Vertiefende Aufgaben 183

10 Datenpfadkomponenten 185

10.1 Lernziele 186

10.2 Multiplexer 186

10.3 Binärzahlendecoder und Demultiplexer 188

10.4 Prioritätsencoder 191

10.5 Code-Umsetzer 193

10.6 Komparator 195

10.7 Hierarchische Strukturmodellierung in VHDL 196

10.8 Addierer 199

10.8.1 Halb- und Volladdierer 199

10.8.2 Ripple-Carry-Addierer 203

10.8.3 Carry-Lookahead-Addierer 206

10.8.4 Kombinierter Addierer/Subtrahierer 209

10.8.5 Addition von Festkommazahlen im Q-Format 209

10.9 Hardware-Multiplizierer 211

10.10 Arithmetik in VHDL 213

10.11 Vertiefende Aufgaben 218

11 Latches und Flipflops in synchronen Schaltungen 221

11.1 Lernziele 222

11.2 Das RS-Latch 222

11.2.1 Basis-RS-Latch 223

11.2.2 Taktzustandsgesteuertes RS-Latch 228

11.3 Das D-Latch (Data-Latch) 230

11.4 D-Flipflops 232

11.4.1 Varianten von D-Flipflops 237

11.5 JK-Flipflop 242

11.6 T-Flipflop 243

11.7 Zweispeicher-Flipflops 244

11.8 RTL-Modellierung synchroner Schaltungen 246

11.9 Zusammenfassung 248

11.10 Vertiefende Aufgaben 249

12 Entwurf synchroner Zustandsautomaten 255

12.1 Lernziele 256

12.2 Formale Beschreibung von Zustandsautomaten 256

12.3 Entwurf eines Geldwechselautomaten 259

12.3.1 Realisierung als Mealy-Automat 259

12.3.2 Realisierung als Moore-Automat 270

12.3.3 Medwedew-Automatenstruktur 275

12.4 Impulsfolgeerkennung mit Zustandsautomaten 275

12.4.1 Implementierung als Moore-Automat 276

12.4.2 Implementierung als Mealy-Automat 278

12.5 Kopplung von Zustandsautomaten 282

12.6 Vertiefende Aufgaben 284

13 Entwurf von Synchronzählern 287

13.1 Lernziele 288

13.2 Manuelle Implementierung von Zählern 288

13.2.1 mod-5-Zähler 288

13.2.2 mod-4-Vorwärts-/Rückwärtszähler 293

13.3 Standardzähler 297

13.3.1 Abhängigkeitsnotation 297

13.3.2 Systematischer VHDL-Entwurf von Zählern 300

13.3.3 Kaskadierung von Standardzählern 304

13.4 Vertiefende Aufgaben 306

14 Schieberegister 311

14.1 Lernziele 311

14.2 Arbeitsweise von Schieberegistern 311

14.3 Serien-Parallel-Umsetzer 313

14.4 Parallel-Serien-Umsetzer 316

14.5 Zähler mit Schieberegistern 319

14.5.1 Ringzähler 319

14.5.2 Johnson-Zähler 321

14.6 Linear rückgekoppelte Schieberegister 324

14.7 Vertiefende Aufgaben 327

15 Synchronisation digitaler Systeme 329

15.1 Lernziele 329

15.2 Kopplung von Signalen in zueinander synchronen Taktdomänen 330

15.2.1 Impulsverkürzung 330

15.2.2 Impulsverlängerung 331

15.3 Synchronisation asynchroner Eingangssignale 335

15.3.1 Synchronisation langer Eingangsimpulse 335

15.3.2 Synchronisation kurzer Eingangsimpulse 339

15.3.3 Asynchrone Resets 340

15.4 Datenaustausch zwischen Teilsystemen 343

15.4.1 Synchrone Datenübertragung 344

15.4.2 Asynchrone Datenübertragung 346

15.5 Vertiefende Aufgaben 355

16 Digitale Halbleiterspeicher 357

16.1 Lernziele 357

16.2 Übersicht 357

16.2.1 Klassifizierung 358

16.2.2 Speicherstrukturen 359

16.2.3 Kenngrößen 360

16.3 Nichtflüchtige Speicher 361

16.3.1 Maskenprogrammierbares ROM 362

16.3.2 PROM 363

16.3.3 EPROM 364

16.3.4 EEPROM und Flash-EEPROM 365

16.3.5 Instanziierung von ROM-Strukturen durch VHDL-Code 366

16.4 Flüchtige Speicher 367

16.4.1 SRAMs 367

16.4.2 DRAMs 370

16.4.3 SDRAM und DDR-RAM 373

16.4.4 Modellierung von SRAM-Speicher in VHDL 375

16.5 FIFO-Speicher 379

16.5.1 VHDL-Modellierung eines Dual-Port-Block-RAMs 382

16.6 Speichererweiterung 386

16.7 Vertiefende Aufgaben 390

17 Programmierbare Logik 393

17.1 Lernziele 393

17.2 PLD-Architekturen 393

17.3 SPLDs 395

17.3.1 PROM-Speicher 396

17.3.2 PLAs 399

17.3.3 PALs 400

17.4 CPLDs 406

17.5 FPGAs 410

17.5.1 Die Spartan-3-FPGA-Familie der Fa. Xilinx 411

17.5.2 Technologische Entwicklungstrends bei FPGAs 419

17.6 Vertiefende Aufgaben 420

18 Anhang 421

18.1 Hinweise zur Verwendung von ModelSim und ISE WebPACK 421

18.1.1 ModelSim Hilfesystem 422

18.1.2 Entwicklungsablauf mit ModelSim 422

18.2 VHDL-Codierungsempfehlungen 434

Literaturverzeichnis 439

Sachregister 443

| Erscheint lt. Verlag | 28.6.2013 |

|---|---|

| Reihe/Serie | De Gruyter Studium |

| Verlagsort | Berlin/München/Boston |

| Sprache | deutsch |

| Themenwelt | Mathematik / Informatik ► Informatik ► Theorie / Studium |

| Technik ► Elektrotechnik / Energietechnik | |

| Schlagworte | Digitaltechnik • Einführung • Lehrbuch • Reichardt • VHDL |

| ISBN-10 | 3-486-75387-8 / 3486753878 |

| ISBN-13 | 978-3-486-75387-5 / 9783486753875 |

| Haben Sie eine Frage zum Produkt? |

Größe: 10,5 MB

DRM: Digitales Wasserzeichen

Dieses eBook enthält ein digitales Wasserzeichen und ist damit für Sie personalisiert. Bei einer missbräuchlichen Weitergabe des eBooks an Dritte ist eine Rückverfolgung an die Quelle möglich.

Dateiformat: PDF (Portable Document Format)

Mit einem festen Seitenlayout eignet sich die PDF besonders für Fachbücher mit Spalten, Tabellen und Abbildungen. Eine PDF kann auf fast allen Geräten angezeigt werden, ist aber für kleine Displays (Smartphone, eReader) nur eingeschränkt geeignet.

Systemvoraussetzungen:

PC/Mac: Mit einem PC oder Mac können Sie dieses eBook lesen. Sie benötigen dafür einen PDF-Viewer - z.B. den Adobe Reader oder Adobe Digital Editions.

eReader: Dieses eBook kann mit (fast) allen eBook-Readern gelesen werden. Mit dem amazon-Kindle ist es aber nicht kompatibel.

Smartphone/Tablet: Egal ob Apple oder Android, dieses eBook können Sie lesen. Sie benötigen dafür einen PDF-Viewer - z.B. die kostenlose Adobe Digital Editions-App.

Zusätzliches Feature: Online Lesen

Dieses eBook können Sie zusätzlich zum Download auch online im Webbrowser lesen.

Buying eBooks from abroad

For tax law reasons we can sell eBooks just within Germany and Switzerland. Regrettably we cannot fulfill eBook-orders from other countries.

aus dem Bereich